2.5/3D Semiconductor heterogeneous integration

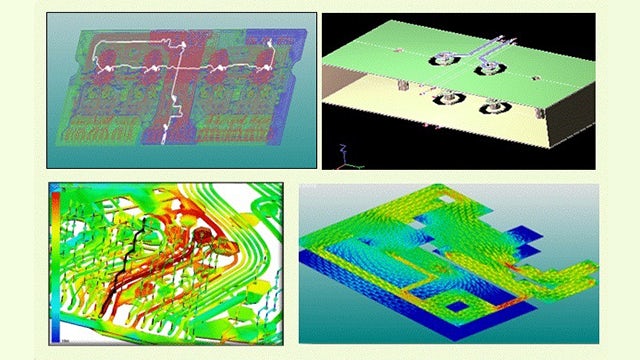

An integrated cockpit driven semiconductor packaging solution that covers everything from prototyping/planning to detailed implementation and signoff for all current and emerging substrate integration platforms. Our solutions help you achieve your silicon scaling and semiconductor performance goals.

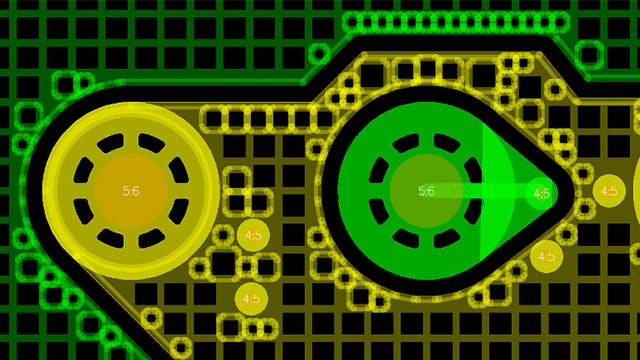

Siemens introduces Innovator3D IC

Siemens Digital Industries Software announces Innovator3D IC, technology that delivers a fast, predictable path cockpit for the planning and heterogeneous integration of ASICs and chiplets using the latest and most advanced semiconductor packaging 2.5D & 3D technologies and substrates in the world.

What drives semiconductor heterogeneous integration?

To get ahead in advanced semiconductor integration you need to consider six key pillars for success.

Integrated system-level prototyping and floorplanning

Heterogeneously integrated chiplet/ASIC designs mandate the need for early package

assembly floorplanning if power, performance, area and cost targets are to be achieved.

Concurrent team-based design

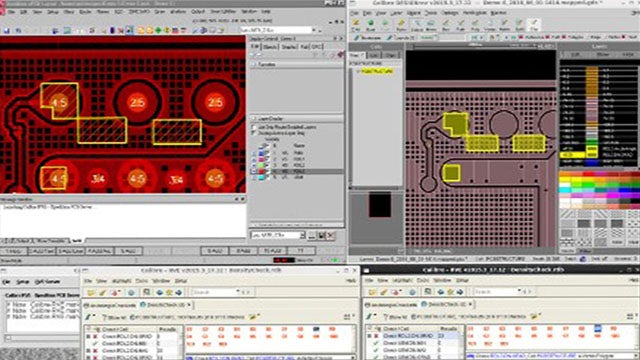

With the complexity of today’s emerging semiconductor packages, design teams need to utilize multiple skilled design resources concurrently and asynchronously in order to meet schedules and manage development costs.

Manufacturing quality throughout the design process

Getting to market faster requires that you have seamless interoperability between the key processes of routing, tuning and metal area fill that deliver results that require minimal signoff cleanup.

Efficient integration of High Bandwidth Memory (HBM)

By using automation and intelligent design-IP replication, designs targeting HPC and AI markets have an increased likelihood of meeting design schedules and quality targets.

Designer productivity and efficiency

With the complexity of today’s IC packages design teams can benefit from true 3D design visualization and editing.

Design capacity support and performance

As multi chiplet/ASIC designs scale into multi million-pin assemblies it crucial that the design tools can handle this capacity while still delivering productivity and usability.

Advanced semiconductor packaging best practices

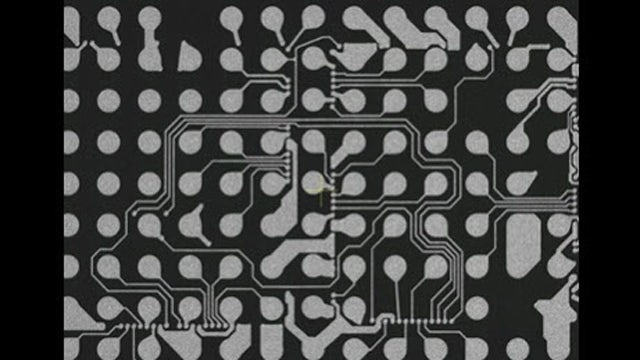

Today, semiconductor packaging design teams must embrace heterogeneous integration using multiple chiplets/ASICs in order address the inflection point of higher semiconductor cost, lower yield, & reticle size limitations.

Semiconductor packaging challenges and solutions

Discover key challenges in semiconductor packaging and explore innovative solutions to support heterogeneous integration.