High Speed Design and Analysis

HyperLynx

HyperLynx is a complete, integrated family of analysis tools for modern PCB design, covering the entire process from schematic capture and exploration through post-layout verification. No matter how simple or complex your design may be, analysis and simulation are easier with HyperLynx.

HyperLynx capabilities

HyperLynx is specifically designed to put the right tool into the right hands. It speeds your analysis journey by allowing you to control the tradeoff between analysis speed and accuracy, thereby providing the most accurate simulations at the most appropriate times. HyperLynx capabilities include:

The most popular analysis tool for high-speed designs

HyperLynx is interfaced to many PCB Layout systems, allowing you to quickly import and set up your PCB design for analysis. Whatever layout tool you use, high-speed post-layout verification is easier with HyperLynx.

With HyperLynx, there’s no need for additional software

HyperLynx provides a complete set of analysis tools, pre-integrated, from a single vendor, along with proven workflows and examples. No switching formats, no isolated specialists, no bottlenecks.

Integrated part of our PCB design flow

HyperLynx works even better when it's part of a design flow that uses our design capture and PCB layout tools, integrated within a full PCB design flow from schematic capture through prototype fabout and volume manufacturing.

Automated analysis workflows

HyperLynx includes proven analysis workflows that allow you to be productive right "out of the box."

Full system-level post-layout verification

HyperLynx drives full-system post-layout verification using key technologies:

- Automated post-layout topology extraction

- Integrated 2D, 2.5D and 3D electromagnetic modeling

- Component and standards-based, protocol-specific simulation

Progressive verification finds issues faster and easier

HyperLynx progressive verification feature analyzes a design in stages, locating issues early, without involving SI and PI experts.

- Expert-based rule checks

- Standards-based compliance analysis

- Vendor-specific simulation

Scalable from novice to expert

HyperLynx offers a broad variety of analysis capabilities and automated flows that make design analysis available to every user, regardless of individual skill level. This improves design quality and accelerates time to market.

HyperLynx applications

HyperLynx is organized into several analysis and verification applications designed to operate as stand-alone solutions, or as integrated components of a complete analysis and verification workflow.

HyperLynx Product Family

The HyperLynx product family is the industry's broadest family of analysis and verification products, covering the complete PCB design flow from initial design capture through post-layout signoff into prototype fabrication. HyperLynx products include:

HyperLynx Schematic Analysis

HyperLynx Schematic Analysis quickly checks your design schematics for logical and electrical issues and provides detailed feedback on potential issues, allowing you to resolve issues early in your design cycle.

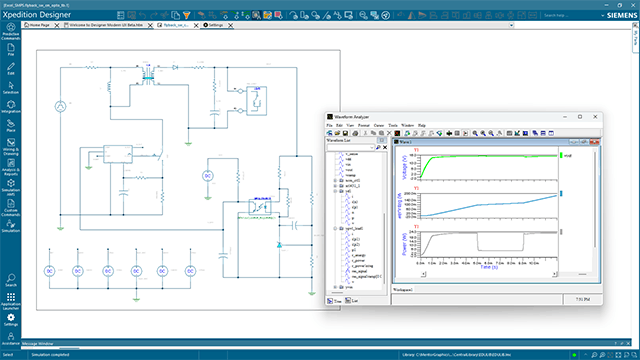

HyperLynx AMS

The HyperLynx Analog/Mixed-Signal simulator lets you model, simulate and optimize behavior for those parts of your design that contain analog circuitry.

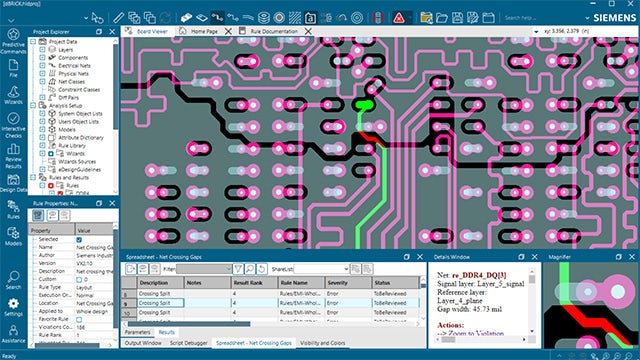

HyperLynx DRC

HyperLynx DRC performs fast, thorough rules-based inspection of PCB layouts, finding issues in minutes that would take hours or days to find with simulation.

HyperLynx Power Integrity

HyperLynx PI performs both DC and AC power delivery analysis to ensure the components on your board get the required power at the required frequencies.

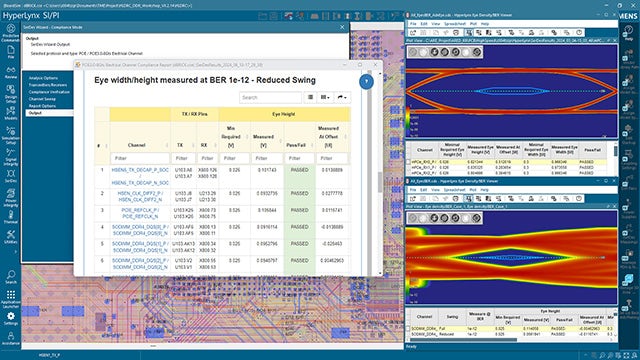

HyperLynx Signal Integrity

HyperLynx Signal Integrity performs advanced analysis of DDR interfaces, SerDes-based serial links and general purpose signals to tell you which signals will work, which will fail, and by how much.

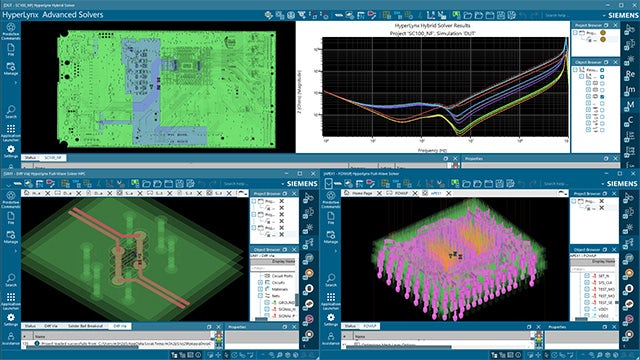

HyperLynx Advanced Solvers

HyperLynx Advanced Solverx provide advanced 3D EM modeling that is tightly integrated with HyperLynx analysis flows, including full-wave, hybrid and quasi-static analysis.

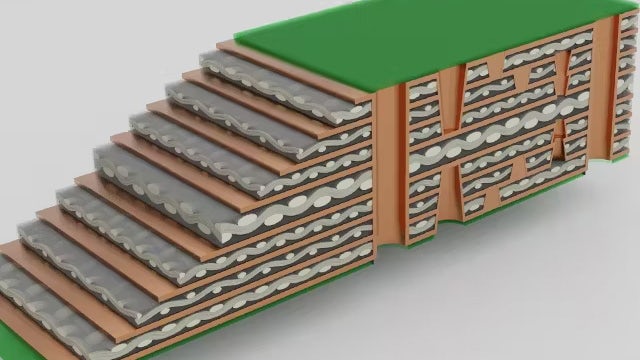

Z-Planner Enterprise

Z-planner Enterprise is a stackup planning tool to help manage and optimize stackup design. The stackup calculator, DFMs, wizard and materials library all focus on reducing PCB material costs without sacrificing performance.