3D integrated circuits (3D ICs) are emerging as a revolutionary approach to design, manufacturing and packaging in the semiconductor industry. Offering significant advantages in size, performance, power efficiency and cost, 3D ICs are poised to transform the landscape of electronic devices. However, with 3D ICs come new design and verification challenges that must be addressed to ensure successful implementation.

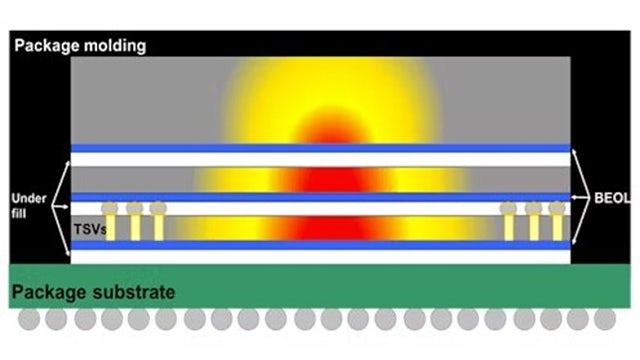

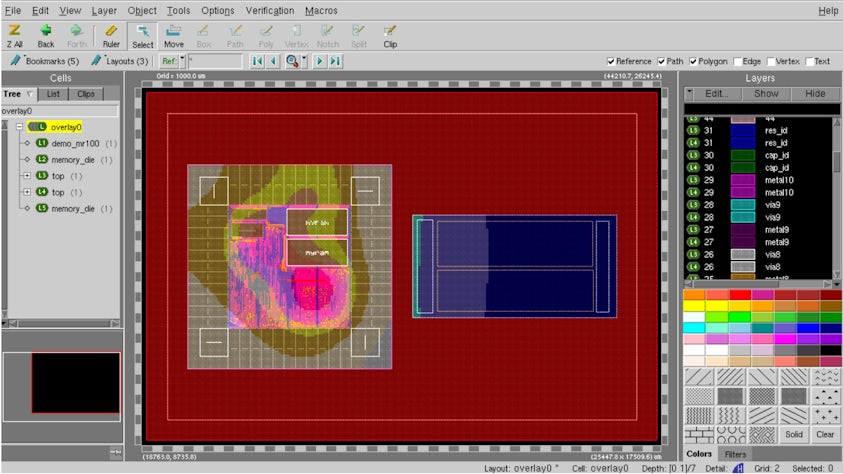

The primary challenge is ensuring that active chiplets in a 3D IC assembly behave electrically as intended. Designers must start by defining the 3D stack-up so that design tools can understand the connectivity and geometric interfaces across all components in the assembly. This definition also drives automation of cross-die parasitic coupling impacts, laying the groundwork for 3D-level analysis of thermal and stress impacts.

This paper outlines key challenges and strategies in 3D IC design. Multiphysics issues in 3D ICs, such as the combined effects of electrical, thermal, and mechanical phenomena, are more complex than in 2D designs, and new materials used in 3D ICs introduce unpredictable behaviors, requiring updated design methods that account for vertical stacking and interconnects. Thermal analysis is especially important as heat buildup can affect both electrical performance and mechanical integrity, compromising reliability. Implementing shift-left strategies can prevent costly rework by integrating multiphysics analysis early in the design process, while iterative design allows for refining decisions as more accurate data becomes available. The content is aimed at IC designers working on chiplets or 3D ICs, package designers creating advanced multi-die packages, and anyone interested in the latest advancements in 3D IC technology.

.jpg?auto=format,compress&w=640&h=360&q=60&fit=crop)