Correctly modeling a PCB stackup is the foundation of accurate simulation results. Not all stackups are created equal; the exact materials, properties and dimensions used to fabricate the board must be specified for simulation results to match the actual PCB. This information is usually not correct in the PCB database received from layout designers, and it often changes when a particular fabricator is selected to build the board.

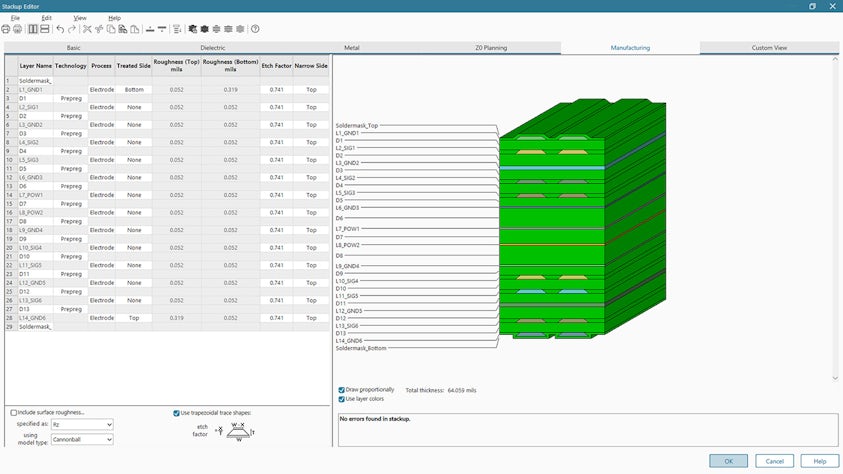

The HyperLynx stackup editor lets designers manage stackup data to ensure that it reflects the board as it will be built. They can view and edit the properties for each layer independently, specify trace surface roughness and changes to trace geometries as the result of manufacturing. The HyperLynx stackup editor can import stackup data directly from Z-Zero Z-Planner, which allows designers to select materials from a large material database and model the effects of different board assembly schemes.