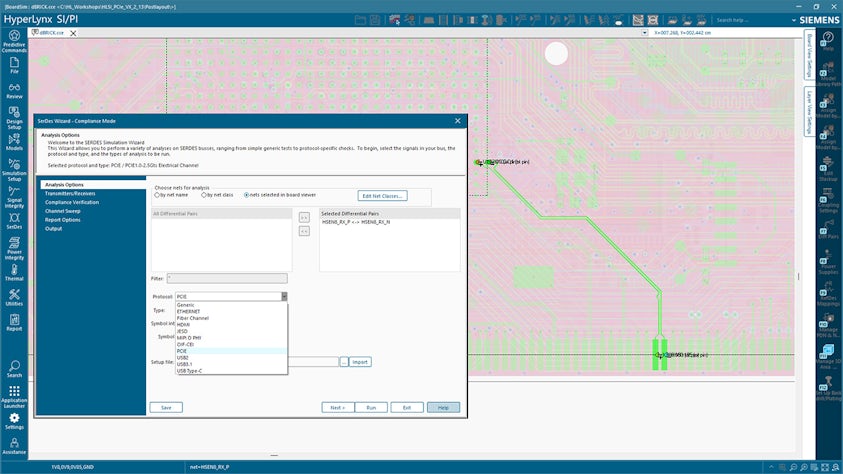

HyperLynx supports over 250 different protocols and variants from the Ethernet, Fiber Channel, HDMI, JESD, MIPI D-PHY, OIF-CEI, PCI-e and USB families.

Serial links must conform to requirements in associated standards specification documents. These specifications lay out requirements for the transmitter (Tx) device and IC package, pin-to-pin system level interconnect and the receiver (Rx) device and IC package. These documents are long (often hundreds of pages) and detailed. Understanding just one standard completely is a huge task - but there are dozens of them, with hundreds of variants.

Siemens experts study each of these standards to create simulation setups that configure HyperLynx to perform the correct analysis flow and report the metrics associated with each standard protocol.

Each analysis type is specified via a built-in configuration file that automatically sets up channel speed, modulation, stimulus encoding, analysis flow and metric reporting for both Compliance Analysis and IBIS-AMI simulation. These configuration files can be copied and modified using a built-in editor, and new configurations can be added when available. HyperLynx also includes a set of "generic" setups that are useful for quick what-if analysis and prototyping support for new protocols.