Why use Tessent RTL Pro?

Shortens design cycles

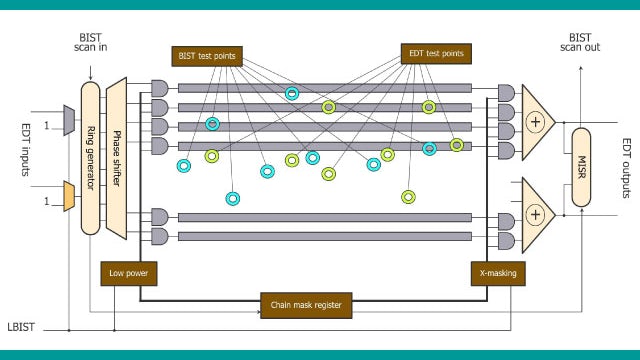

Build on the Tessent RTL editing capabilities with RTL Pro, which enables designers to leverage leading-edge tools to continue their shift-left push, enabling VersaPoint and LBIST-OST test points to be inserted in the design RTL.

Enhances “shift-left” strategies

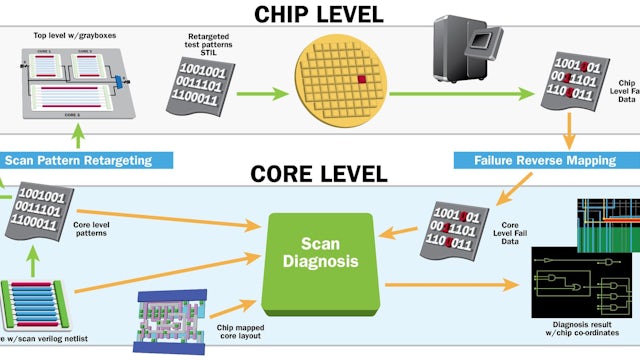

Continue to use third-party synthesis and verification tools for optimization of added DFT logic during synthesis leaving only scan insertion to be performed at gate level. The logic inserted is RTL; the output design remains RTL.

Reduces volume of data

Insert x-bounding and VersaPoint test point technology into the design RTL, to improve coverage and reduce pattern count.

Supports needs of downstream tools

Use the same RTL for synthesis and verification to improve performance and shorten design time. Writing test-inserted RTL allows synthesis tools to optimize DFT logic. Verification tools work faster when used with RTL.

Shift left to do more, earlier in design flows

Automate the analysis and insertion of test points, wrapper cells and x-bounding logic earlier in the design flow, at the RTL level. Tessent RTL Pro handles complex Verilog and SystemVerilog constructs and maintains the look and feel of the original RTL design. Resulting RTL output simplifies the flow of downstream tools allowing synthesis to account for the test logic added to the design.