Why Tessent MemoryBIST?

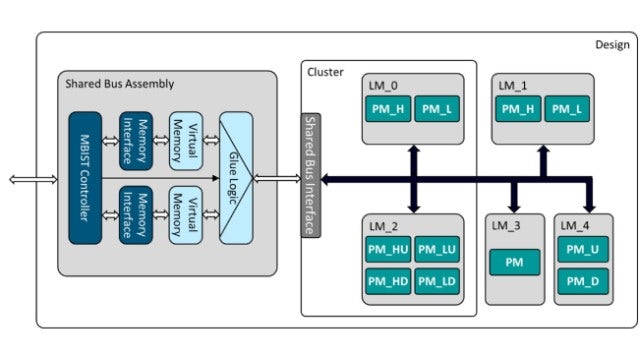

Tessent MemoryBIST, an industry-leading memory built-in self-test, includes a uniquely comprehensive automation flow that provides design rule checking, test planning, integration, and verification all at the RTL or gate level.

ECC-based memory repair

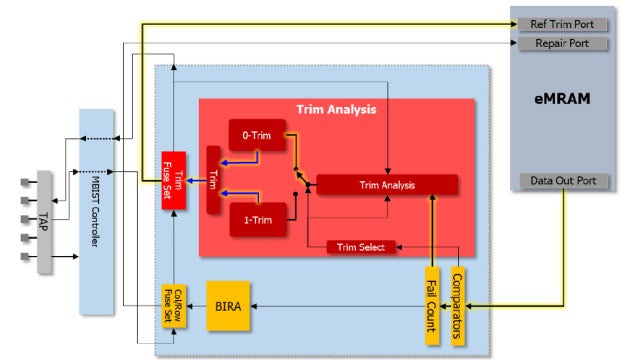

Tessent MemoryBIST ECC enhances reliability, improves test quality and safeguards against aging defects. Its customizable pass/fail criteria allow for an optimal combination of memory redundancy and error-correcting code.

Non-volatile memory application

Tessent MemoryBIST NVM provides flexible test and repair, decreases manufacturing test costs and enhances reliability. Automated NVM-specific algorithms enable specialized access modes and work with the ECC-aware option as needed.

Advanced BIST access port

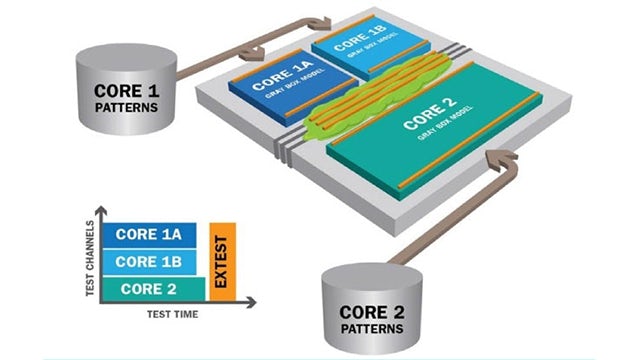

The advanced BAP provides a configurable interface to optimize in-system testing. It also supports a low-latency protocol to configure the memory BIST controller, execute Go/NoGo tests, and monitor the pass/fail status.

Algorithm programmability

Memory test algorithms can be hardcoded into the Tessent MemoryBIST controller, then applied to each memory through run-time control. This lets you select shorter test algorithms as the manufacturing process matures.

Power-aware on-chip self-repair

The Tessent MemoryBIST repair option eliminates the complexities and costs associated with external repair flows. It tests and permanently repairs all defective memories in a chip using virtually no external resources.

Maximize test quality with Tessent MemoryBIST

Watch Etienne Racine, Tessent Product Manager, talk about how Tessent MemoryBIST can help maximize test quality, minimize test time, improve yield and repair memories with its flexible architecture.