Why Tessent BoundaryScan?

Tessent BoundaryScan logic can be accessed throughout the life of the IC, including manufacturing test at all package levels, silicon debug, and system verification to detect defects before shipment, reducing field support costs and increasing customer satisfaction.

Complete boundary scan and TAP controller integration

Automatically generates and integrates RTL code for the TAP controller and boundary scan cells into the design RTL. Generates scripts for logic synthesis, simulation testbenches and test patterns for manufacturing test.

Supports multiple formats

Tessent Boundary scan supports IEEE 1149.1 custom boundary scan cells and contactless I/O test and has an option for 1149.6 boundary scan support.

IEEE 1687 IJTAG interoperability

Automatically connects IJTAG networks and instruments to the newly inserted TAP controller and generates resulting Instrument Connectivity Language files. I/O tests are generated in Procedural Description Language (PDL) format.

Learn more

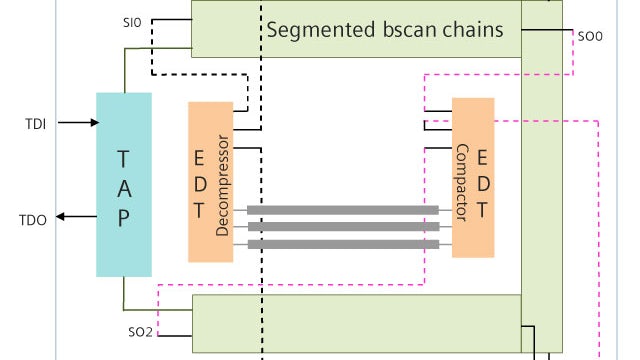

Tessent Embedded Boundary Scan

This video shows the implementation flow of Tessent Boundary Scan (1149.1) at the top level and Tessent Embedded Boundary Scan at the physical block level in Tessent Shell.

Tessent Training > Tessent Integrated Flow

Learn how to implement MBIST, BoundaryScan, IJTAG, Scan Insertion and TestKompress into your design to obtain high test quality using multiple Tessent tools.