Effective debug and trace with Tessent UltraSight-V

Tessent UltraSight-V is an end-to-end solution consisting of embedded IP and software designed to provide comprehensive, efficient debugging and trace capabilities that integrates with industry standard tools to further empower embedded software engineers in developing high-performance embedded software.

Tessent UltraSight-V demo

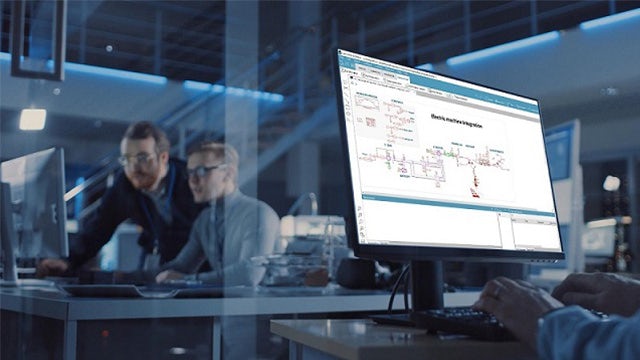

In this demonstration, you can learn how you can use Tessent UltraSight-V along with VSCode to perform RISC-V debug and trace. We will show examples of run control using GDB and OpenOCD, processor trace based on the RISC-V E-Trace standard, and system memory access using optimized ELF upload.

How Seagate improves debug & optimization with Tessent

Listen to Richard Bohn, engineering director of advanced IP development at Seagate Technology, describe some of Seagate's challenges and how they use Tessent Embedded Analytics products to improve their debug and optimization.

A complete trace solution for RISC-V processors

Complex systems are prone to imperfect software behaviors. Use our fully featured RISC-V trace solution, Tessent Enhanced Trace Encoder, to monitor the program execution of a CPU in real time.

Learn more

Lauterbach TRACE32 RISC-V trace

Learn how to perform RISC-V trace using Lauterbach’s TRACE32 solution and the Tessent Enhanced Trace Encoder in this demo video.