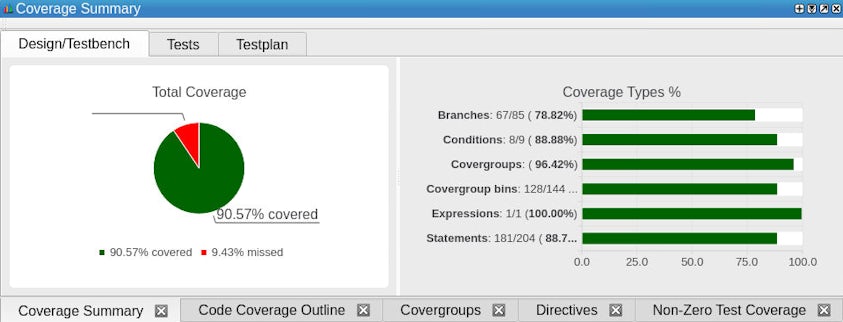

Catapult Coverage provides HLS-aware code coverage that, unlike software-centric coverage tools, recognizes how design constructs and HLS directives impact the resulting post-HLS hardware and thus takes these into consideration when collecting and reporting code coverage on HLS design source. Examples include function inlining and loop unrolling directives. Catapult Coverage also supports needed coverage types on HLS design source such as Condition and Focused Expression (FEC) coverage plus array access coverage.