Copper layer creation

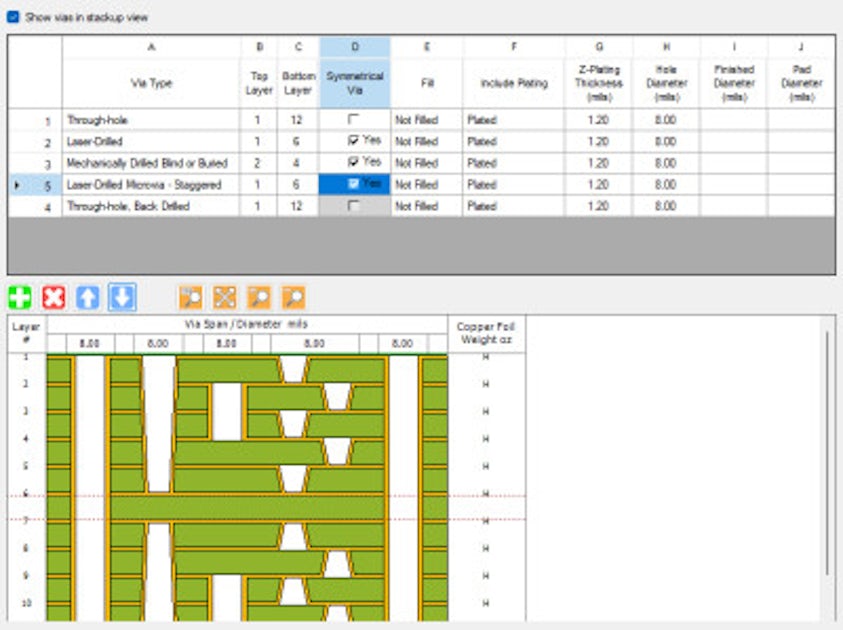

Z-planner Enterprise is useful for defining sequentially laminated HDI stackups.

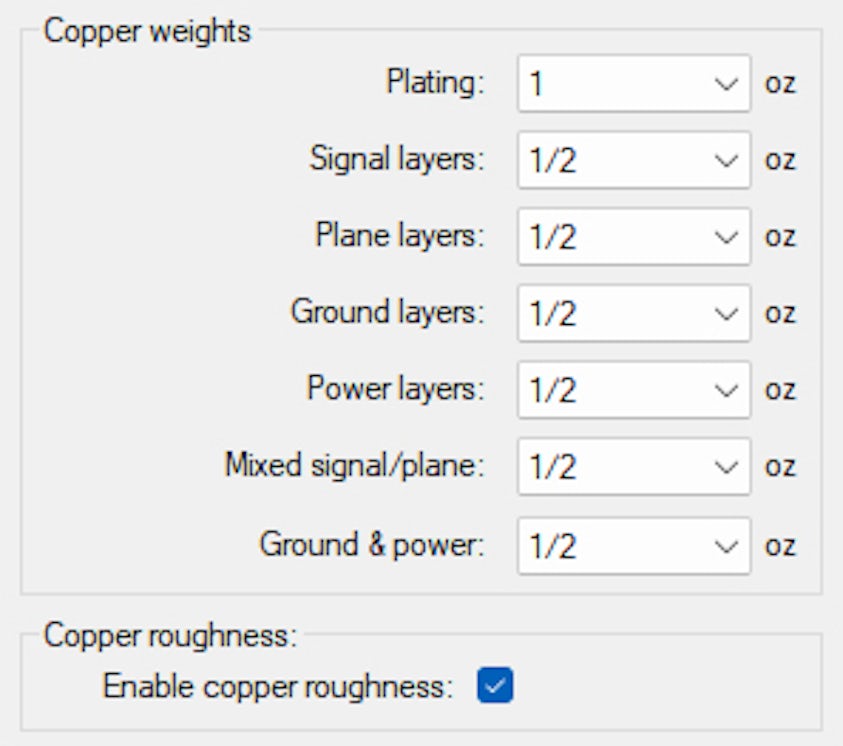

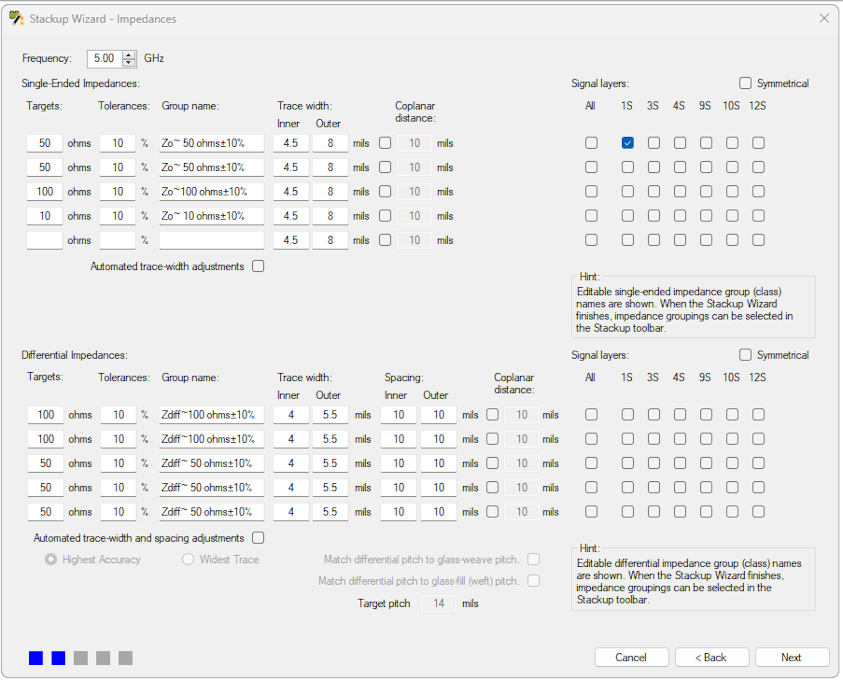

The stackup wizard generates an optimized stackup based on the number, sequence and copper weight of individual layers as they correspond to copper weight, trace width, spacing and etchback values. Z-planner Enterprise can generate stackups with a standard single lamination cycle or create a sequentially laminated stackup, including blind and buried via fabrication, multiple prepregs on build-up layers, as well as the associated plating.

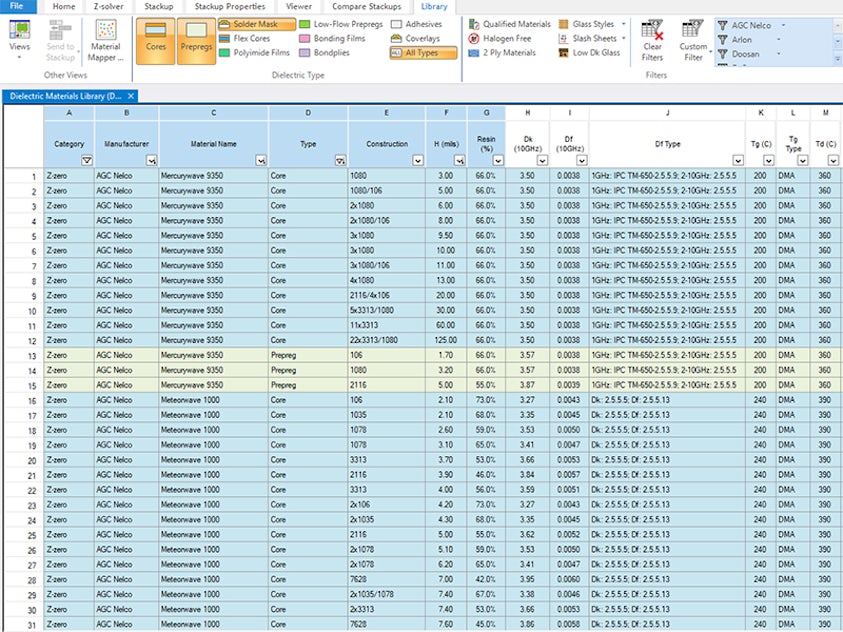

Z-planner Enterprise’s materials library contains copper (Cu) roughness values for both sides of the foil as measured in Rx (um) values.