HyperLynx Schematic Analysis eliminates the need for manual schematic reviews and increases overall workflow efficiency by providing automated schematic reviews in parallel with design capture. By adopting a ‘right first time’ design flow, HyperLynx Schematic Analysis reduces development, testing and warranty costs, eliminating 50-70% of design respins caused by schematic errors and poor design practices.

HyperLynx Schematic Analysis enables full inspection of all nets on a schematic using an extensive intelligent model component library. Schematic analysis saves design teams hundreds of hours of visual inspection and lab debug time by analyzing each net within a schematic. This analysis executes rapidly prior to your schematic freeze milestone, such that layout may commence with highest confidence of first-pass success.

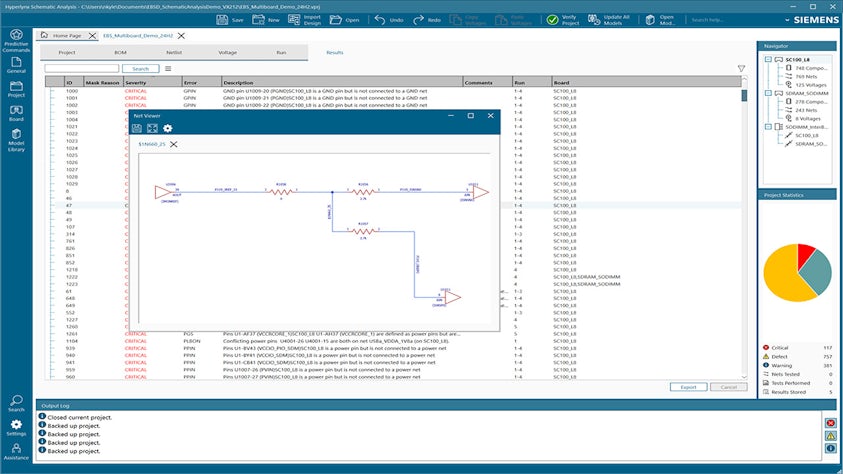

HyperLynx Schematic Analysis doesn’t rely on a symbol library like a native schematic checker would; instead, it takes the manufacturer part number of each component straight from your Bill of Materials and references a library built from vendor datasheets to find issues like capacitor derating failures; incorrect symbols; missing pull ups; etc. Schematic Analysis identifies these issues without the need for time-intensive manual effort. The end output is a compact graphical representation of critical, defect and warning situations from which you can cross probe directly into the schematic to resolve on the fly.

Schematic analysis is performed in parallel with design capture, with errors highlighted directly in the schematic. It can also be performed on electronic designs after they have been released into the market to improve the quality of the electronic design, to increase yield, and to decrease product returns.

Key rule checks

- Complete extended net verification (through series resistors, switches, AC-coupling)

- Full multi-board and backplane interface verification

- IO compatibility checks for maximum, minimum and logic thresholds

- Address & data bus errors (MSB to LSB, bus source, etc.)

- Verifies external passive requirements

- Unconnected mandatory pins identification

- Power/ground plane connection verification

- Differential connectivity checks

- IO net connectivity validation (missing driver/receiver)

- Pin function compatibility tests (resets, I2C swapping, etc.)

- Symbol mismatch (to datasheet)

- Derating capacitors, resistors & diodes

…And many more