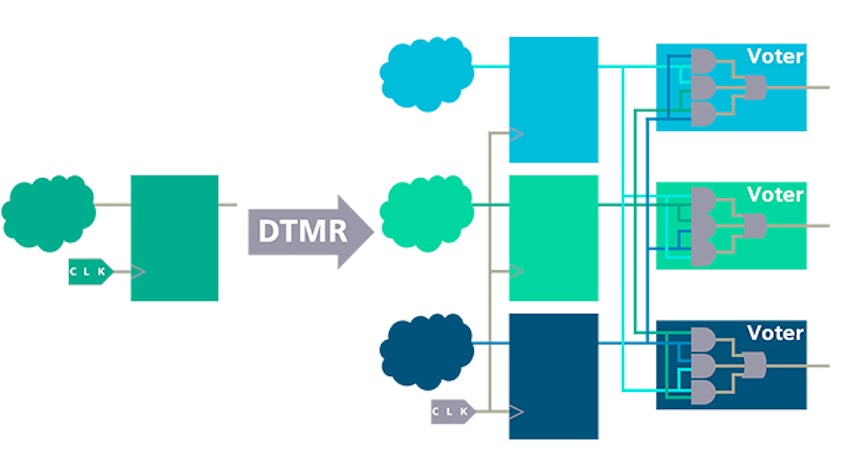

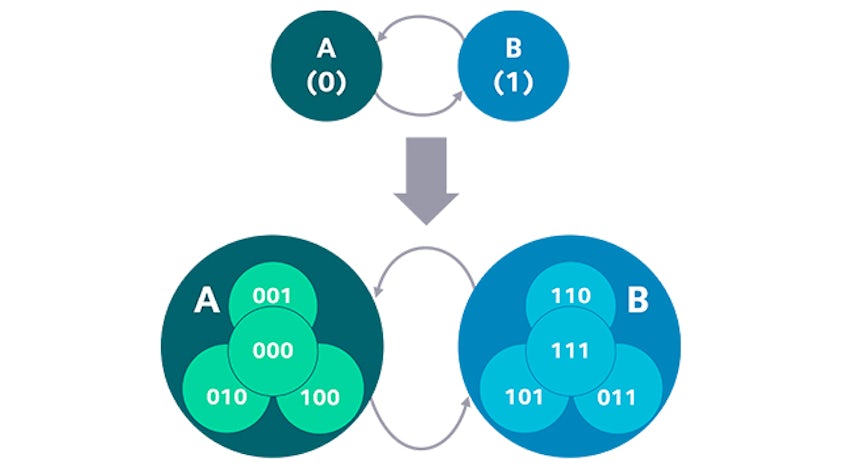

TMR is the most popular mitigation strategy used for protection from SEUs/SETs in FPGAs. Precision Hi-Rel provides the widest selection of TMR modes - LTMR, DTMR, GTMR & intelligent Selective TMR (iSTMR), enabling users to trade-off between safety, area and performance. Inserting TMR at the synthesis level provides greater user control and superior QoR.