Overview

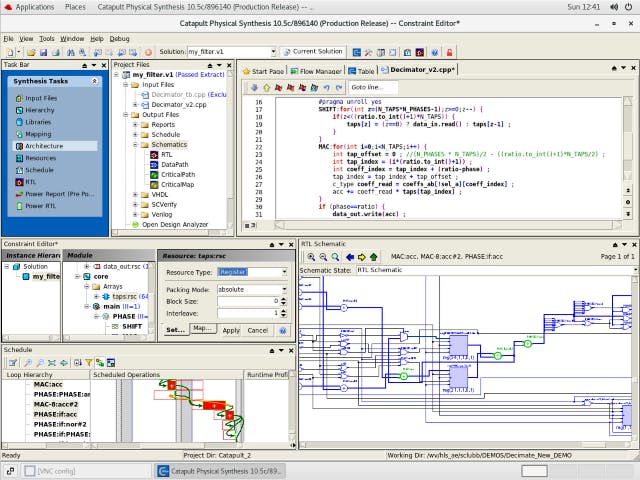

Catapult Physical Aware

Taking Catapult to the next level by partnering with advanced RTL Synthesis technologies such as Synopsys DC-NXT, plus Siemens EDA’s Oasys and Precision FPGA Synthesis. Catapult delivers improved QoR for Performance, Power and Area with latest process technologies.

A Closer Connection To Physical RTL Synthesis

As geometries decrease, estimation and interpolation of RTL operator synthesis for advanced FPGAs or ASIC multiVT effects becomes harder. To build optimal RTL, HLS must neither over-pipeline, nor under-pipeline the output RTL in order to tune the Performance, Power and Area results downstream.

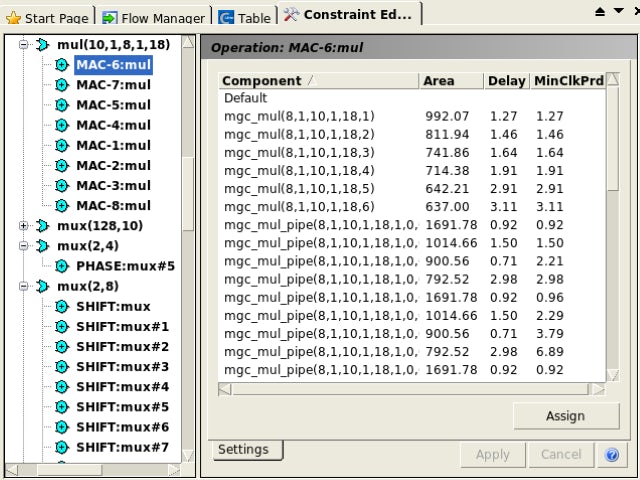

Getting An Exact Answer For Every Operator

On The Fly Characterization uses downstream physically aware synthesis tools to build a complete area/performance tradeoff of every operator needed in your design. Advanced caching across multiple users and designs reduces iterative runtime, while providing superior results for modern geometries. MultiVT option choices round out the optimization trade-offs.

Trading Power, Performance & Area

MultiVT libraries deliver a wide range of power and performance. High performance gate level implementations come at a cost of power and area. Designers need a mechanism to drive VT usage to achieve the optimum tradeoff for their specific needs. Catapult delivers a multiVT approach for On-The-Fly Characterization with modern process technologies.

Catapult on-demand training

The Catapult High-Level Synthesis (HLS) on-demand training library contains a set of learning paths with modules to introduce engineers to HLS and high-level verification.

High-Level Synthesis and Verification Group

A group to discuss the finer points of design and verification using Siemens EDA HLS and HLV tools. Join the discussion on new topics, features, content and technical experts.

HLSLibs

A free and open set of libraries implemented in standard C++ for bit-accurate hardware and software design. It's an open community for exchange of knowledge and IP for HLS that can be used to accelerate both research and design.

HLS Design and Verification Blog

Blog covering next generation high-level synthesis (HLS) design and verification methodologies and techniques.

Catapult Support

Access detailed documentation, releases, resources and more.

EDA consulting

Helping you achieve maximum business impact by addressing complex technology and enterprise challenges with a unique blend of development and design experience and methodology expertise.