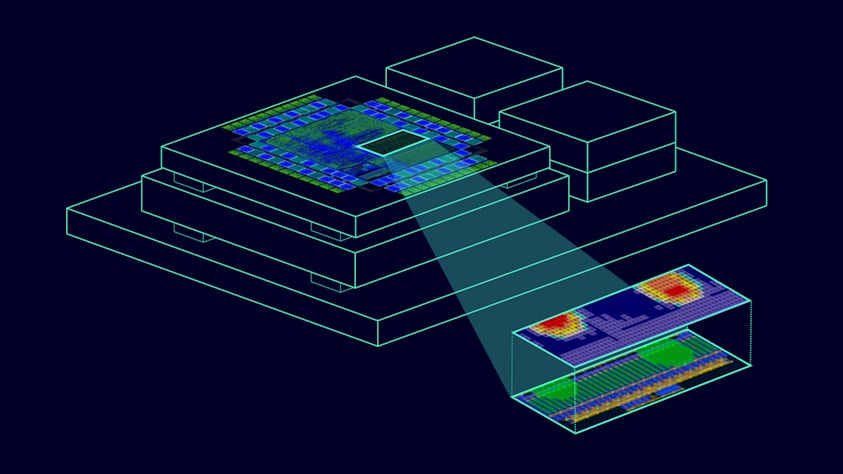

As the industry transitions toward advanced 3D IC architectures and heterogeneous integration, managing thermo-mechanical stress is essential for product quality and long-term reliability. Calibre 3DStress enables design and packaging teams to simulate, analyze and disposition stresses imparted on the chip during or after the packaging process, ensuring that potential failure risks—such as warpage, cracking, and mobility changes—are identified and mitigated well before tapeout or manufacturing.

With Calibre 3DStress, early analysis helps chip designers ensure that package-induced stress does not compromise chip reliability or electrical behavior. Actionable analysis results support IP and device placement decisions in the context of the full 3D IC assembly. Once the design is finalized, sign-off analysis makes certain that thermo-mechanical stress complies with required specifications. Integrated into the broader Siemens Calibre multi-physics platform—alongside tools such as Calibre 3DThermal, mPower, Solido, and Innovator3D IC —Calibre 3DStress brings together multi-domain simulation and accelerates robust decision-making.

Calibre 3DStress is ideal for experienced Calibre users actively designing advanced 3D ICs, particularly those facing tight device mobility constraints, chip-package co-design and close attention to transistor-level reliability.