Overview

IC Package Simulation

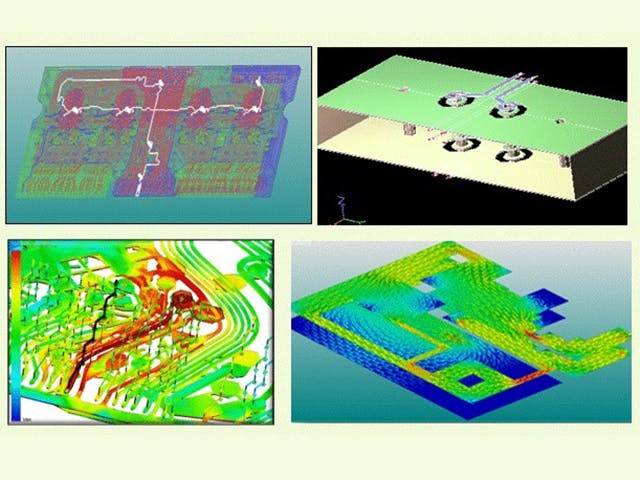

Comprehensive analysis of die/package coupling, signal integrity/PDN performance, and thermal conditions.

Physical Implementation & Manufacturing Handoff

Signal integrity/PDN issues are found, investigated, and validated. 3D thermal modeling and analysis predicts airflow and heat transfer in and around electronic systems.

Package Simulation key features

Comprehensive analysis of die/package coupling, signal integrity/PDN performance, and thermal conditions. Signal integrity/PDN issues are found, investigated, and validated. 3D thermal modeling and analysis predict airflow and heat transfer in and around electronic systems.

Analysis of voltage drop & IC switching noises

Power distribution networks can be analyzed for voltage drop and switching noise issues. Identify potential DC power delivery issues such as excessive voltage drop, high current densities, excessive via currents and associated temperature rise including co-simulation for signal/power/thermal impact. Results can be reviewed in graphical and report formats.

Analyze signal integrity (SI) issues in the design cycle

HyperLynx SI supports general-purpose SI, DDR interface signal integrity and timing analysis, power-aware analysis, and compliance analysis for popular SerDes protocols. From pre-route design exploration and “what-if” analysis through detailed verification and sign-off, all with fast, interactive analysis, ease-of-use, and integration with Package Designer.

Comprehensive SERDES analysis

SERDES interface analysis and optimization include FastEye diagram analysis, S-parameter simulation, and BER prediction. These utilize automatic channel extraction, interface-level channel compliance verification, and pre-layout design exploration. Together, these automate SERDES channel analysis while retaining accuracy.

Intra-die & Inter-die parasitic extraction

For an analog design, the designer must simulate the system circuitry, including parasitics. For a digital design, the designer must run static timing analysis (STA) on the complete package assembly, including parasitics. Calibre xACT provides accurate parasitic extraction of TSVs, front and backside metal, and TSV to RDL coupling.

Full-3D electro-magnetic-quasi-static (EMQS) extraction

Full package model creation with multi-processing for faster turnaround time. It is ideally suited for power integrity, low-frequency SSN/SSO, and complete-system SPICE model generation while accounting for skin effect impact on resistance and inductance. As an integral part of Xpedition Substrate Designer, it is immediately available to all package designers.

2.5/3D IC package thermal modeling

Modeling heterogeneous 2.5/3D IC-package thermal chip-package-interactions is important for several reasons. Designing a large high power device, e.g. a AI or HPC processor without considering how to get the heat out is likely to lead to problems later on, resulting in a sub-optimal packaging solution from cost, size, weight and performance perspectives.