Overview

Questa HL-SYC Expansion

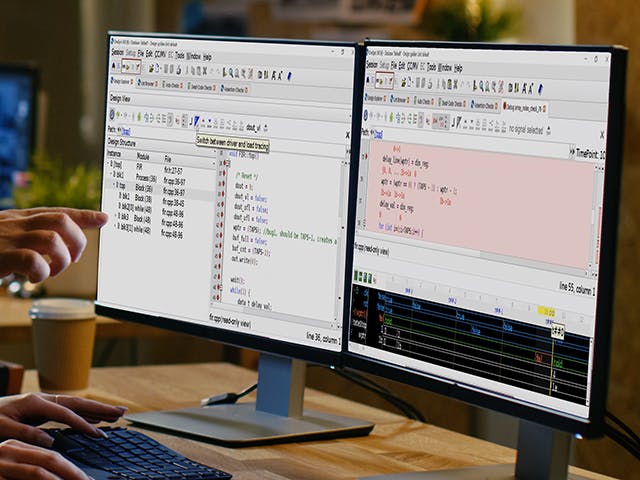

High-level design verification with Questa HL-SYC expansion helps eliminate issues before synthesis by starting verification earlier in the flow. Diminishes the simulation workload, streamlining the creation of an optimized input code for HLS with an array of automated checks prior to synthesis.

Get in touch with our sales team 1-800-547-3000

Bring Formal-based verification to your SystemC/C++ HLS

Earlier and more effective SystemC/C++ verification and issue detection can be achieved through automated and exhaustive formal verification. Provides clearer messages and directions for code improvement, ensuring comprehensive coverage metrics.

- Enables the elimination of design defects before High-Level Synthesis (HLS), allowing for verification to commence much earlier in the design process.

- Reduces significantly the simulation effort required for both SystemC and Register Transfer Level (RTL) designs.

- Optimizes the HLS input code before synthesis, ensuring a more efficient and error-free design pipeline.

Provides an arithmetic analysis solution for C++ and SystemC and automatically performs two primary checks on SystemC fixed point and integral data types:

- Ensures that no registers in the datapath overflow due to inadequate bit width when handling large calculations

- Ensures that no bits are wasted in the datapath by verifying that the correct precision is set on all registers, preventing unused Most Significant Bits (MSBs)

Supports other number representations, including vendor-specific fixed point data implementations, by utilizing pre-packaged assertion libraries

Upcoming and on-demand events

View all available Formal Verification video recordings at the Verification Academy.

Ready to talk to someone today?

We're standing by to answer your questions.

Get in touch with our sales team 1-800-547-3000

Learn more

Verification Academy

Verification Academy provides the skills necessary to mature an organization's functional verification process capabilities, providing a methodological bridge between high-level value propositions and the low-level details.

Verification Horizons blog

Insight and updates on concepts, values, standards, methodologies and examples to assist with the understanding of what advanced functional verification technologies can do and how to most effectively apply them.

Verification Horizons

The Verification Horizons publication provides concepts, values, methodologies and examples to assist with the understanding of what advanced functional verification technologies can do and how to most effectively apply them.