Overview

Oasys-RTL Synthesis

Oasys-RTL addresses the need for higher capacity, faster runtimes, improved QoR, and physical awareness by optimizing at a higher level of abstraction and using integrated floorplanning and placement capabilities.

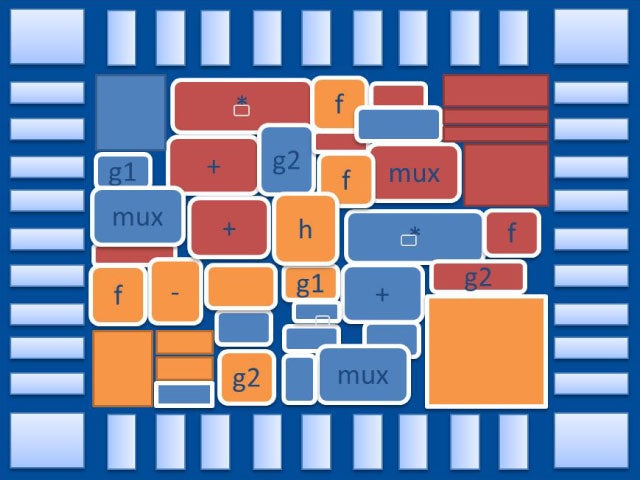

Fast, High-Quality Physical RTL Synthesis

Oasys-RTL provides better quality of results by enabling physical accuracy, floorplanning, and fast optimization iterations to get to design closure on time.

Power-Aware Synthesis

The power-aware synthesis capabilities include support for multi-threshold libraries, automatic clock gating, and UPF based Multi-VDD flow. During synthesis Oasys-RTL inserts all the appropriate level shifters, isolation cells and retention registers depending on the power intent as defined in the UPF.

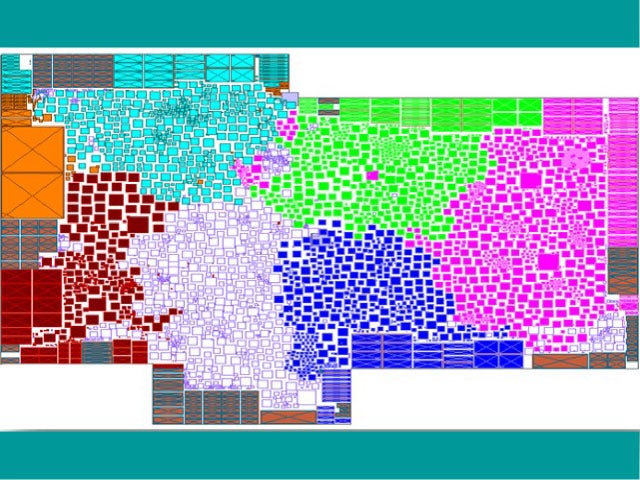

Create a Floorplan Directly From RTL

Oasys-RTL can create a floorplan directly from the design RTL using design dataflow and timing, power, area, and congestion constraints. It considers regions, fences, blockages and other physical guidance using the advanced floorplan editing tools and automatically places macros, pins, and pads.

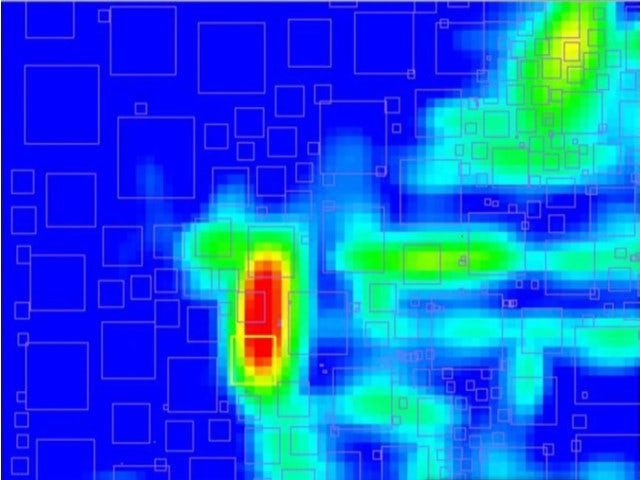

Unique Placement-First Method

Rather than synthesizing first, then trying to optimize the gates, Oasys-RTL concurrently optimizes higher-level RTL partitions where it has a greater ability to converge on the best solution.

Join the IC design community

Join the discussion on new topics, features, content and technical experts.

Training and support

Access detailed user application notes, training resources and more.

EDA consulting

Helping you achieve maximum business impact by addressing complex technology and enterprise challenges with a unique blend of development and design experience and methodology expertise.