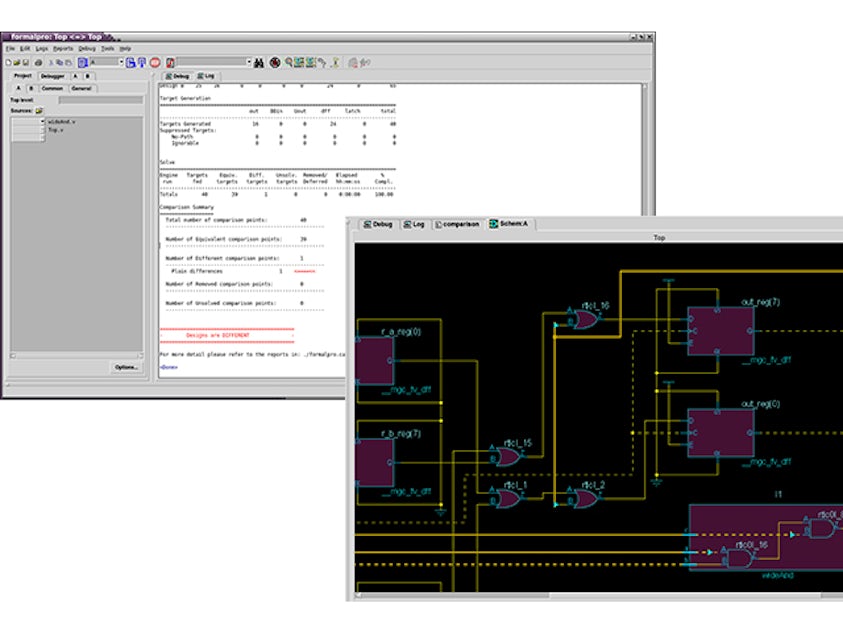

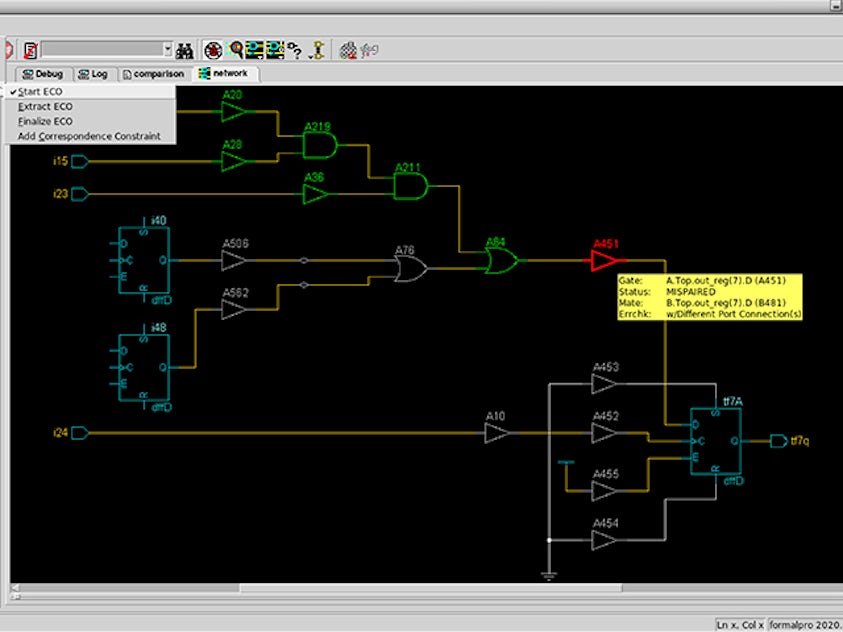

Rapid verification of multi-million gate designs and dramatic reduction in verification time using static formal verification techniques. Fastest route to correct design with a comprehensive debug tool that identifies the location/cause of errors and the unique “what-if” capability to investigate design modifications within the existing verification session.