Overview

Calibre Pattern Matching

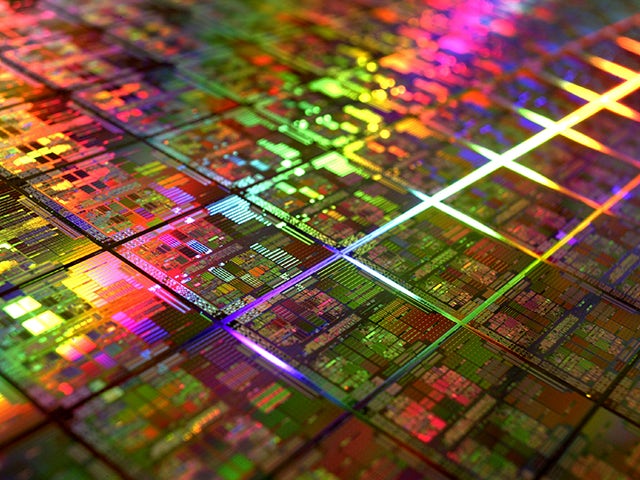

At advanced nodes, SoC designers must balance customization of SRAM for better performance against potential impacts on yield. Enhancing SRAM debugging with pattern matching and similarity checking enables SRAM designers to find a better, more precise balance between design flexibility and yield.

Automated pattern classification, matching and debug

The Calibre Pattern Matching tool provides signoff-quality pattern classification, matching, and debugging integrated with the Calibre suite of verification tools. Benefit from the speed and accuracy of pattern matching across all Calibre design and manufacturing flows.

Integrated in the Calibre Platform

The Calibre Pattern Matching tool works within the Calibre platform to enable powerful integrated pattern-based design verification and manufacturing flows. Patterns supplement multi-operational text-based design rule checks, simplifying complex layout descriptions.

Designer assistance for analog and digital flows

Simplify complex design rules requiring multiple-layer device symmetry with a simple call to the Calibre Pattern Matching process. Leverage known good patterns to verify no modification, eliminating lengthy debugging. Pair with Calibre sign-off DRC decks and Calibre RealTime interfaces to streamline verification in all major P&R and design environments.

Supports major foundries’ advanced verification flows

Calibre Pattern Matching technology supports advanced verification flows at all major foundries. From flagging known yield detractors, to identifying IP modifications, to enhancing simulation based flows, Calibre pattern processing enhances many foundry applications.

Ready to learn more about Calibre?

We're standing by to answer your questions! Get in touch with our team today

Call: 1-800-547-3000

EDA consulting

Helping you achieve maximum business impact by addressing complex technology and enterprise challenges with a unique blend of development and design experience and methodology expertise.

Support center

The Siemens Support Center provides you with everything in one easy-to-use location – knowledgebase, product updates, documentation, support cases, license/order information and more.

Design with Calibre blog

The Calibre tool suite delivers accurate, efficient, comprehensive IC verification and optimization across all process nodes and design styles while minimizing resource usage and tapeout schedules.