Overview

Calibre YieldEnhancer

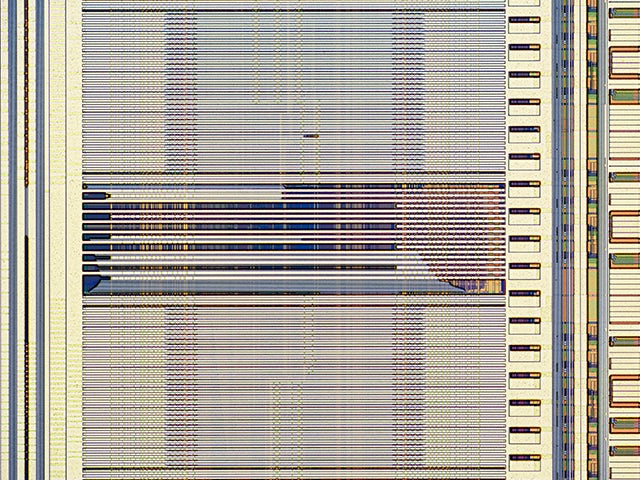

The Calibre YieldEnhancer tool offers an automated approach to layout enhancements that help improve yield without sacrificing area. Calibre YieldEnhancer SmartFill technology addresses new fill challenges at advanced process nodes, including multi-patterning and an ECO fill flow.

Get in touch with our technical team: 1-800-547-3000

Comprehensive Analysis-Based Layout Modification

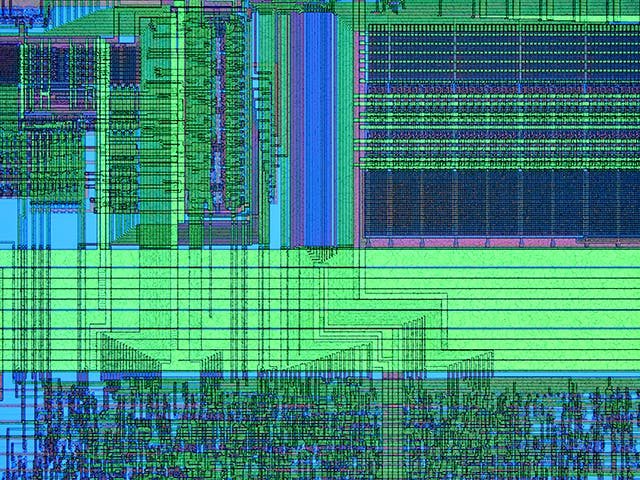

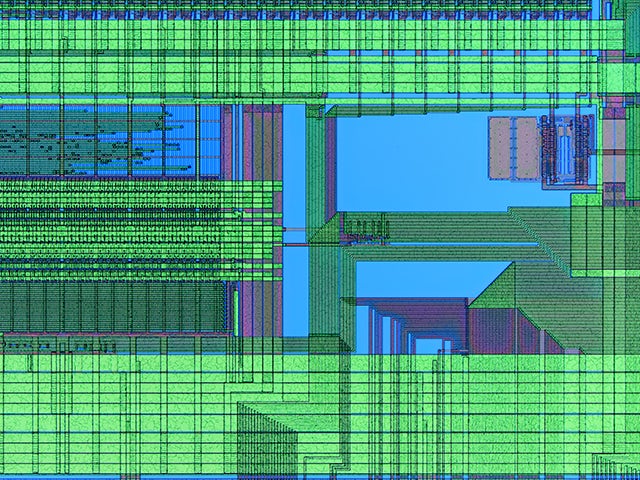

Calibre YieldEnhancer SmartFill functionality combines advanced design analysis with multiple filling solutions for the optimum filling strategy that is correct-by-construction for both digital and analog designs. SmartFill allows designers to satisfy complex IC fill constraints in a single pass.

SmartFill, the Industry’s Leading Fill Solution

Calibre YieldEnhancer SmartFill functionality combines advanced design density analysis with multiple filling solutions for the optimum filling strategy for correct-by-construction results in both digital and custom/analog designs. SmartFill allows designers to satisfy complex IC fill constraints in a single pass, with minimal impact on circuit performance

Optimized Layout Modification That Fits in Design Flows

Calibre YieldEnhancer flows include time-to-market solutions like ECO Fill. The ability to read LEF/DEF and write out changes in an incremental DEF lets the tool fit into all P&R environments

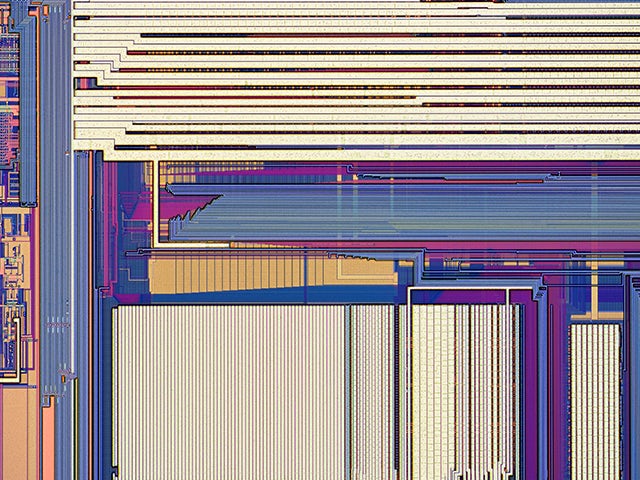

Programmable Edge Modification

Calibre YieldEnhancer programmable edge modification is a collection of automated edge and polygon manipulating functions. DFM Property determines how much to move the shape and then assigns the value onto the polygon. The Calibre YieldEnhancer tool then reads the property and moves the layout.

Ready to learn more about Calibre?

We're standing by to answer your questions! Get in touch with our team today

Call: 1-800-547-3000

Calibre consulting services

We help you adopt, deploy, customize and optimize your complex design environments. Direct access to engineering and product development lets us tap into deep domain and subject matter expertise.

Support center

The Siemens Support Center provides you with everything in one easy-to-use location -

knowledgebase, product updates, documentation, support cases, license/order information and more.

Design with Calibre blog

The Calibre tool suite delivers accurate, efficient, comprehensive IC verification and optimization across all process nodes and design styles while minimizing resource usage and tapeout schedules.