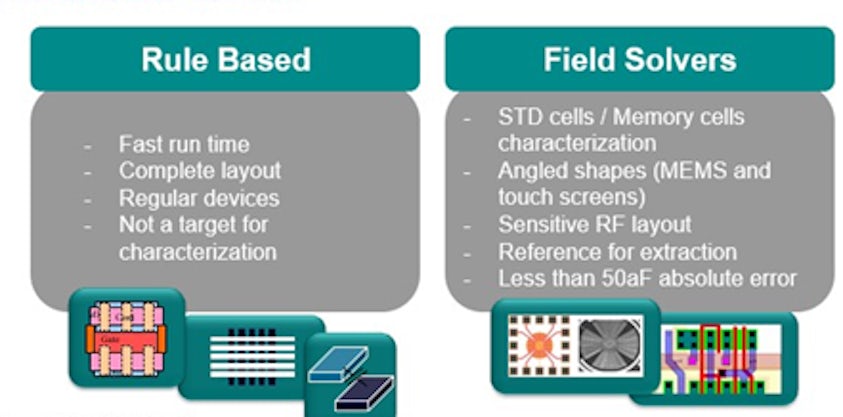

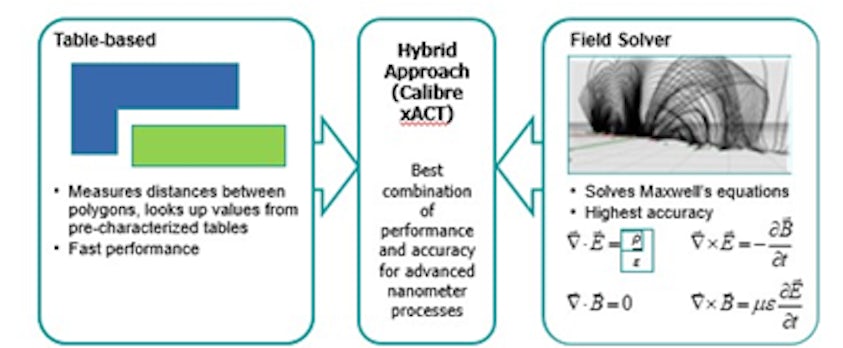

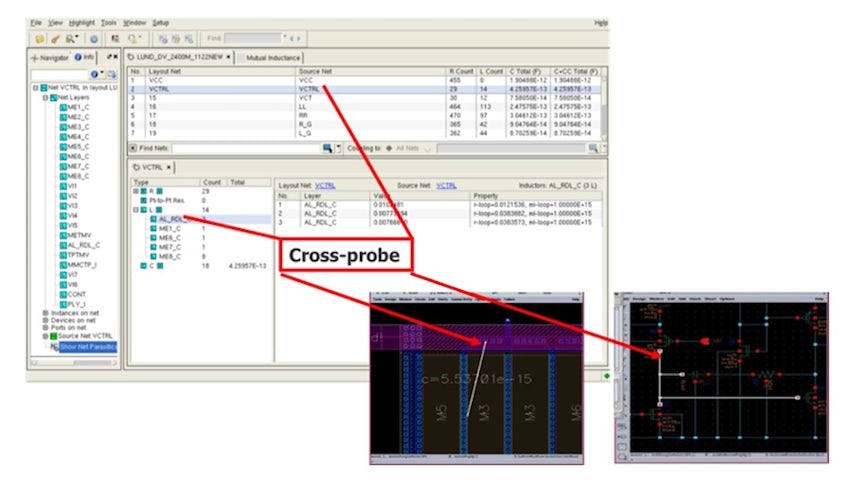

Foundries and EDA vendors must ensure that their PEX rule decks provide accurate extraction. Design companies must ensure the accuracy of their rule-based PEX tool. Correlating rule-based PEX results against a field solver extraction provides reference numbers they can trust, as long as they set up the runs properly to ensure an “apples to apples” comparison.