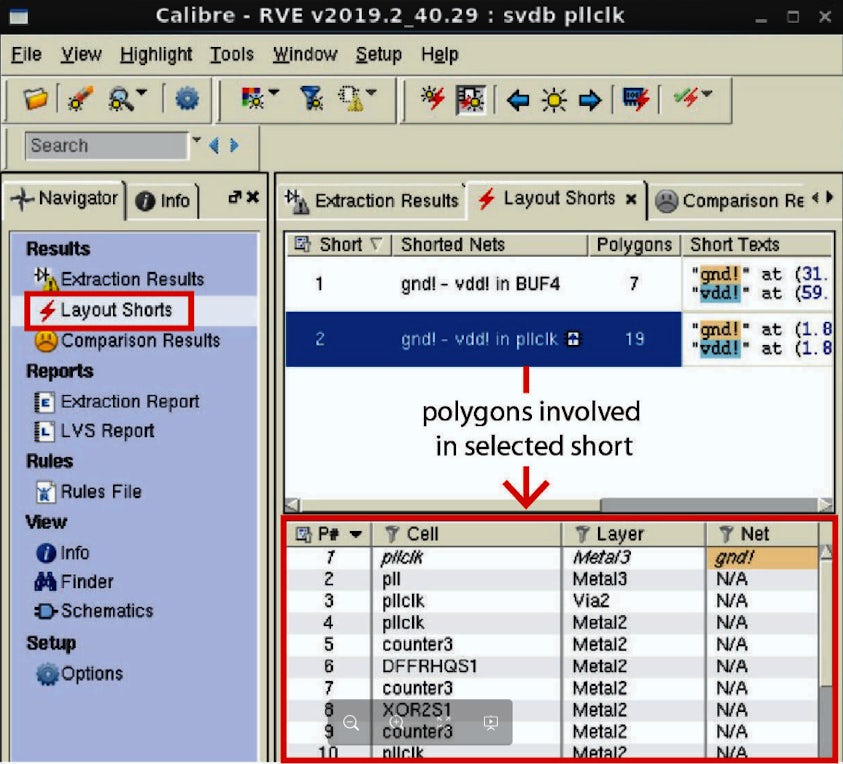

Improving productivity with more efficient LVS debug

Calibre RVE utilities help designers debug and fix LVS errors more quickly, while also eliminating the need for multiple full LVS runs. Interactive short isolation provides a systematic and prioritized shorts debugging process. Fix suggestions in plain text help designers find the root cause of LVS comparison discrepancies, while the ability to highlight discrepancies in both layout and schematic views lets them implement fixes quickly and efficiently.