What’s New in Xpedition IC Packaging- VX.2.10

Xpedition IC Packaging VX.2.10 delivers capabilities targeted at the prototyping, planning, and design of next-generation 2.5/3D heterogeneous packages. Including: support for ultra-high pin count devices, predictive SI/PI analysis during prototyping and planning, and mixed vendor design flows.

Watch the Overview Video

Watch some of the new capabilities in this short video.

What's New in IC Packaging VX.2.10

Watch narrated videos of selected new capabilities.

IC Packaging VX.2.10 Videos

1 / 4

IC Packaging VX.2.10 Videos

1 / 4

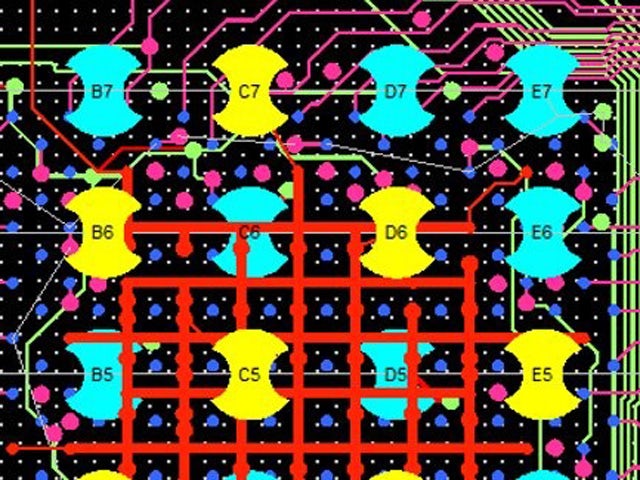

Complex Substrate and Bump Shape Support

HDAP VX.2.10 supports substrate with cutouts/curves and bumps with arcs. This provides more accurate substrate planning allowing for increased device and route densities.

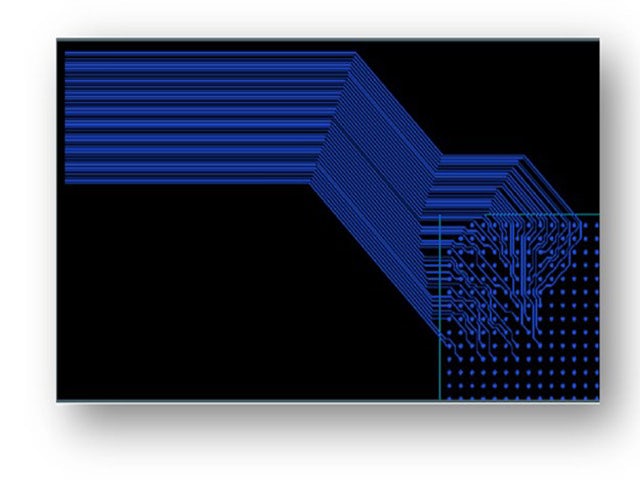

Extend Capabilities for Sketch Planner and Router

VX.2.10 supports extended capabilities for Sketch Planner and Sketch Router. Single pin net support for Blind sketch plans allows sketch plan placement to be done with a single placed part. Additionally, Sketch routing from existing route segments has been improved using the correct netline, continuing in the direction of the existing trace segment.

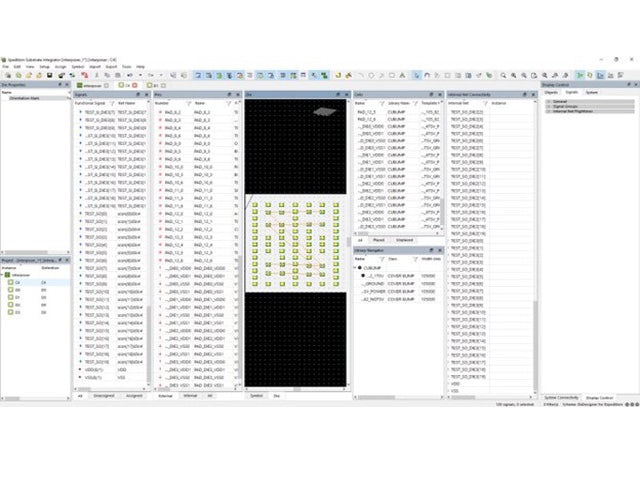

System Level Predictive Analysis

VX.2.10 supports system level predictive analysis during prototyping and planning. Early access to SI and DC IR drop analysis reduces the risk of late-stage design spins. Early fabrication DRC during substrate implementation reduces signoff rework during tapeout.

Cleaner More Intuitive GUI/UX for xSI

VX.2.10 supports cleaner more intuitive GUI/UX for xSI, reducing adoption ramp to proficiency, productivity, and designer satisfaction.

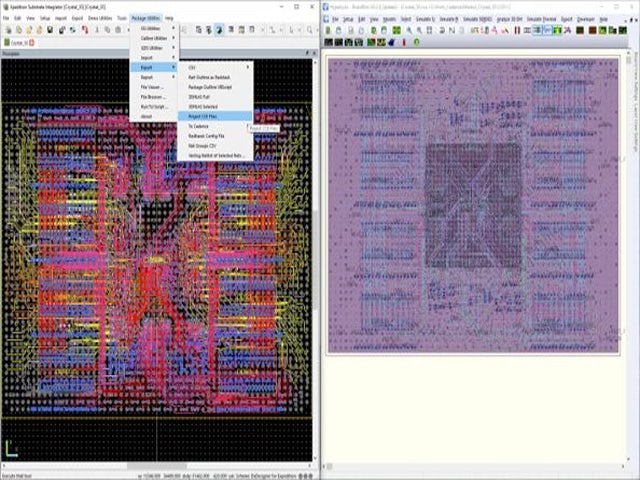

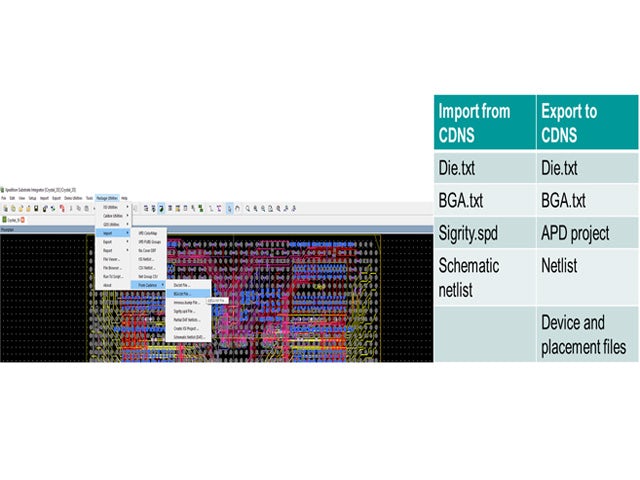

Collaboration Utilities Enable Mixed Flow Support

VX.2.10 collaboration utilities enable mixed-flow support, enabling an effective Siemens/Cadence design flow.

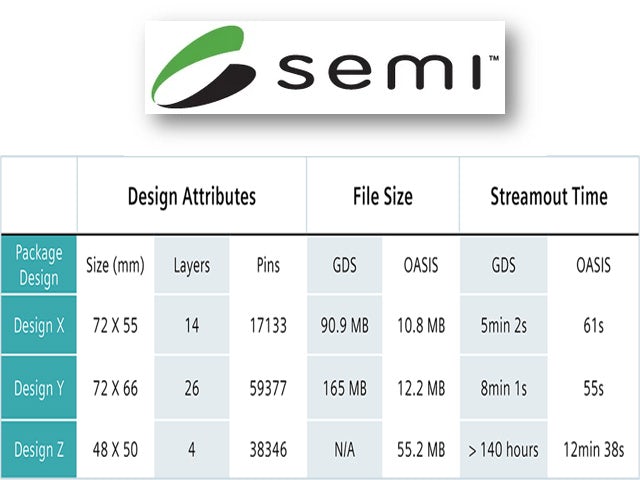

Oasis Manufacturing Format Output

VX.2.10 open artwork system interchange standard (OASIS) is a hierarchical mask layout data format that yields much smaller file sizes than GDSII and is much faster to generate. You also have an option to export mask layers in OASIS format for substrate fabrication.

Download the Release

Note: The following is a condensed summary of the release highlights. Siemens customers should refer to the Release Highlights on Support Center for detailed information regarding all new features and enhancements.