July 1 & 3 | Hyderabad & Bengaluru

all

India User2User Verification Forums

User2User Verification Forums are an opportunity to learn and connect with fellow D&V engineers using Questa tools and advanced RTL verification methodologies. Join us!

Register and learn

Recorded webinars and events

Watch recorded events and on-demand webinars at your own convenience.

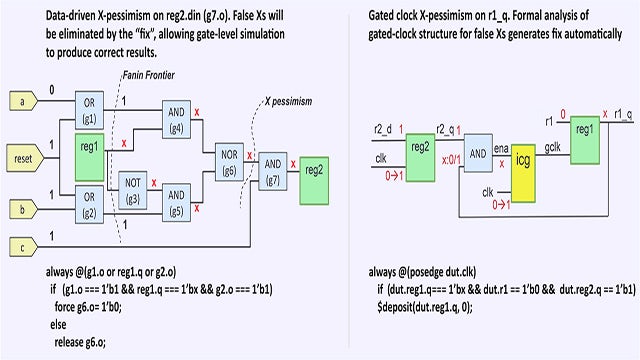

FORMAL VERIFICATION VIRTUAL EVENT

all

osmosis Aerospace and Defense 2024 | April 23-24, 2024

osmosis A&D is about sharing the success in using formal techniques to address demanding verification of DO-254 compliant and other high-consequence systems - along with delivering sneak-previews of our future product roadmaps

Select presentations available on-demand